## United States Patent [19]

## Tang et al.

#### [54] ARRANGEMENT FOR PARALLEL PROGRAMMING OF IN-SYSTEM PROGRAMMABLE IC LOGICAL DEVICES

- [75] Inventors: Howard Tang, San Jose, Calif.; Cyrus Tsui, Vancouver, Wash.

- [73] Assignee: Lattice Semiconductor Corporation, Hillsboro, Oreg.

- [21] Appl. No.: 957,311

- [22] Filed: Oct. 5, 1992

- [51] Int. Cl.<sup>5</sup> ..... H03K 19/177

#### [56] References Cited

#### **U.S. PATENT DOCUMENTS**

|           |         | Canter 307/465 X           |

|-----------|---------|----------------------------|

| 4,858,178 | 8/1989  | Breuninger 307/465 X       |

| 4,866,508 | 9/1989  | Eichelberger et al 307/465 |

| 4,870,302 | 9/1989  | Freeman 307/465.1 X        |

| 4,876,466 | 10/1989 | Kondou et al 307/465       |

## US005329179A [11] Patent Number: 5,329,179 [45] Date of Patent: Jul. 12, 1994

5,237,218 8/1993 Josephson ...... 307/465

Primary Examiner—David R. Hudspeth Attorney, Agent, or Firm—Skjerven, Morrill, MacPherson, Franklin & Friel

### [57] ABSTRACT

A plurality of programmable logic devices are connected in parallel to a programming command generator. A device selector connects individual devices with the programming command generator, thereby permitting the individual devices to be programmed without routing the programming data through other devices. In an alternative embodiment, an identification code is used to place the individual device in a condition to receive programming data. Using the teachings of this invention, programming data may initially be entered into a plurality of devices, and then the data entered in all the devices may be used to program the devices simultaneously. This procedure requires less time than entering data and giving each device the execute command in sequence.

#### 6 Claims, 9 Drawing Sheets

Fig. 9A

#### ARRANGEMENT FOR PARALLEL **PROGRAMMING OF IN-SYSTEM** PROGRAMMABLE IC LOGICAL DEVICES

#### FIELD OF THE INVENTION

This invention relates to in-system programmable IC logic devices and, in particular, to a parallel arrangement for programming such devices.

#### BACKGROUND OF THE INVENTION

In-system programmable (ISP) logic devices offer the advantage that they may be programmed in place, without removing them from the system in which they are 15 connected. This saves time and makes them particularly suitable for systems that are dynamically reconfigurable.

U.S. Pat. No. 4,870,302 illustrates (FIGS. 8A and 8B) two systems for programming a group of ISP devices. 20 In each system, the ISP are connected in series, so that the programming data must be transferred through each device in the series before arriving at the intended destination device. Similarly, U.S. application Ser. No. 07/695,356, commonly owned and incorporated by 25 conductor Corporation. reference herein, describes an arrangement for programming a group of ISP devices that are connected in series. These arrangements suffer from the disadvantage that the devices can only be programmed one at a time and that the data must often be routed through several 30 devices before it reaches its destination.

#### SUMMARY OF THE INVENTION

In accordance with this invention, a programming 35 command generator is connected in parallel with a group of ISP logic devices. A device selector is used to connect the programming command generator to a desired ISP device, thereby allowing the programming data to be delivered directly to that device without passing through intermediate devices. Several configurations for the device selector are described, including a demultiplexer, a state machine-controlled demultiplexer, a switch matrix, and a state machine-controlled switch matrix. These possibilities are not exhaustive, 45 however; other equivalent arrangements will be apparent to those skilled in the art and are included within the broad principles of this invention.

Normally it takes longer to program an ISP logic device than it does to enter the programming data into 50 programmable logic devices. ISP devices 1, 2 and 3 are the device. Accordingly, an advantage of this arrangement is that the programming data may first be read into each of the devices separately, and then all of the devices can be programmed simultaneously. This substantially reduces the amount of time required to program 55 selector is a demultiplexer. A programming command the devices.

In an alternative embodiment, the device selector is omitted and the device to be programmed is selected by transmitting an identification code unique to that device so as to establish communication between that device 60 alone and the programming command generator.

The broad scope and varied possibilities of this invention will become apparent from the detailed description, which refers to the following drawings.

#### BRIEF DESCRIPTION OF THE DRAWINGS

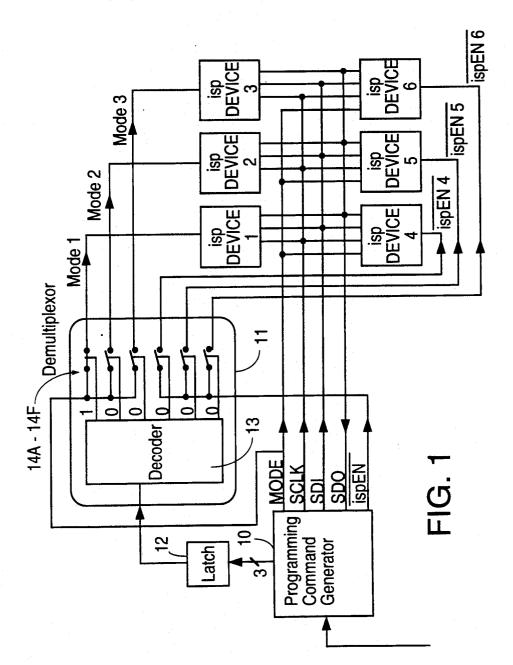

FIG. 1 illustrates a block diagram of an embodiment of the invention which includes a demultiplexer.

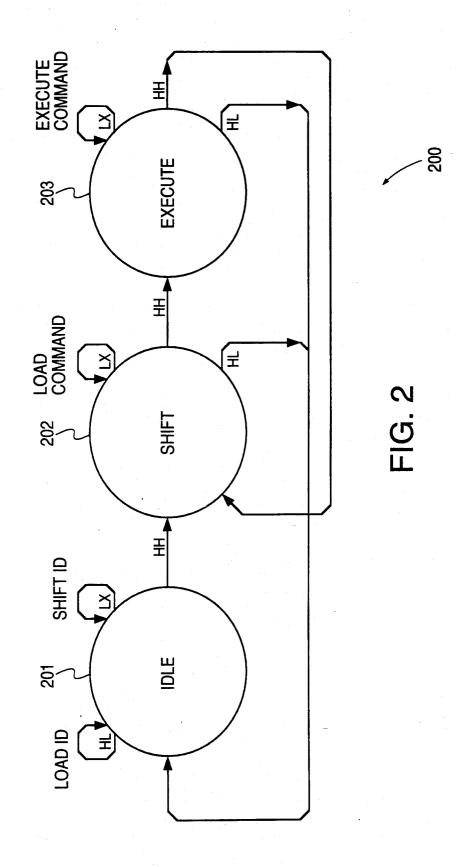

FIG. 2 illustrates a flow chart of the state machine in the ISP devices.

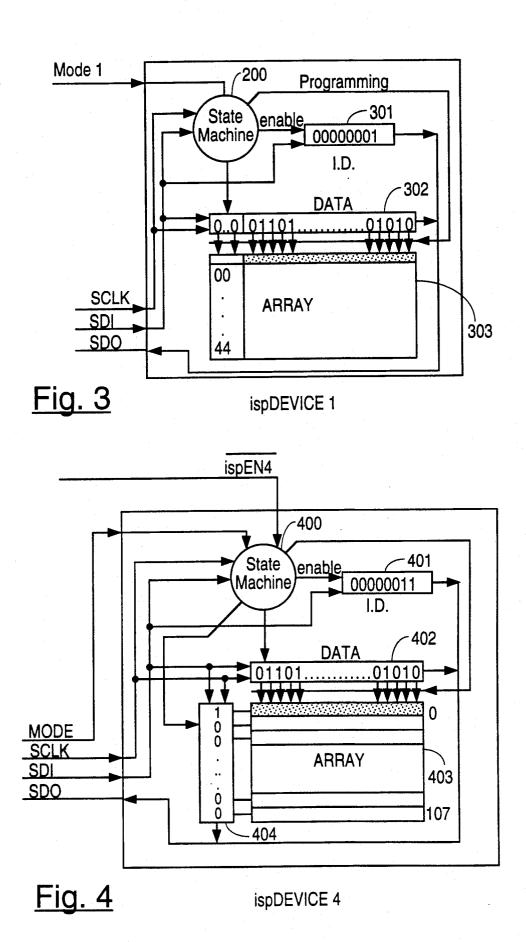

FIG. 3 illustrates the general structure of an ISP device having four input signals.

FIG. 4 illustrates the general structure of an ISP device having five input signals.

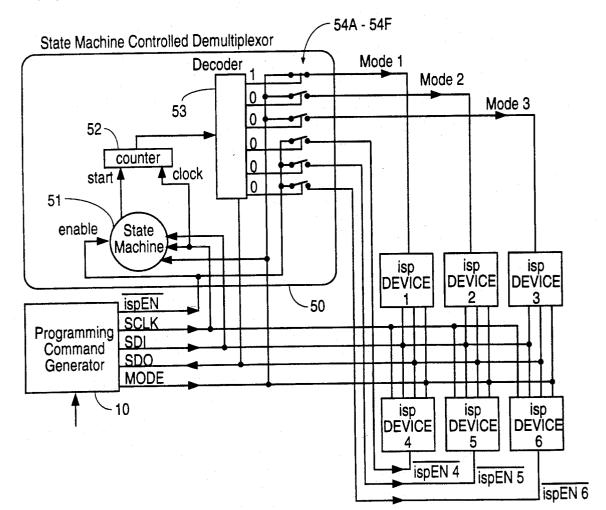

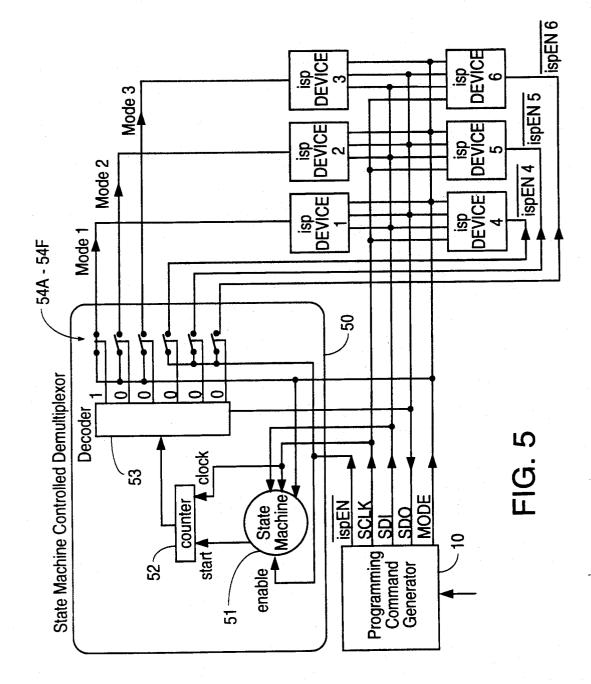

FIG. 5 illustrates a block diagram of an embodiment of the invention which includes a state machine-controlled demultiplexer.

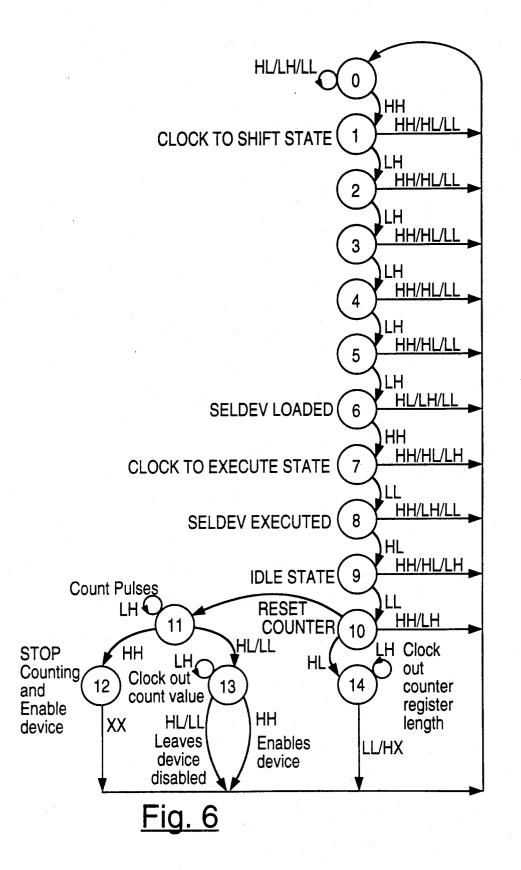

FIG. 6 illustrates a flow chart of the state machine in 10 the state machine-controlled multiplexer of FIG. 5.

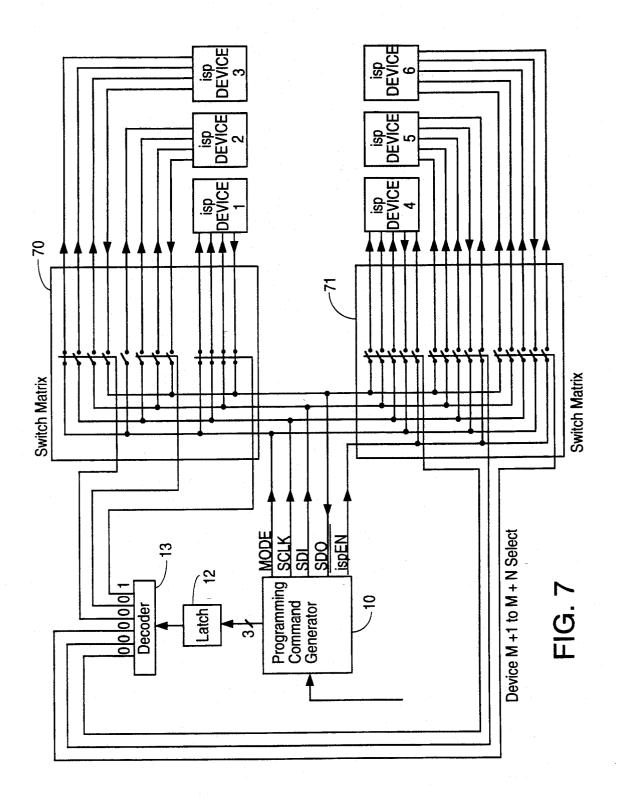

FIG. 7 illustrates a block diagram of an embodiment of the invention which includes a switch matrix.

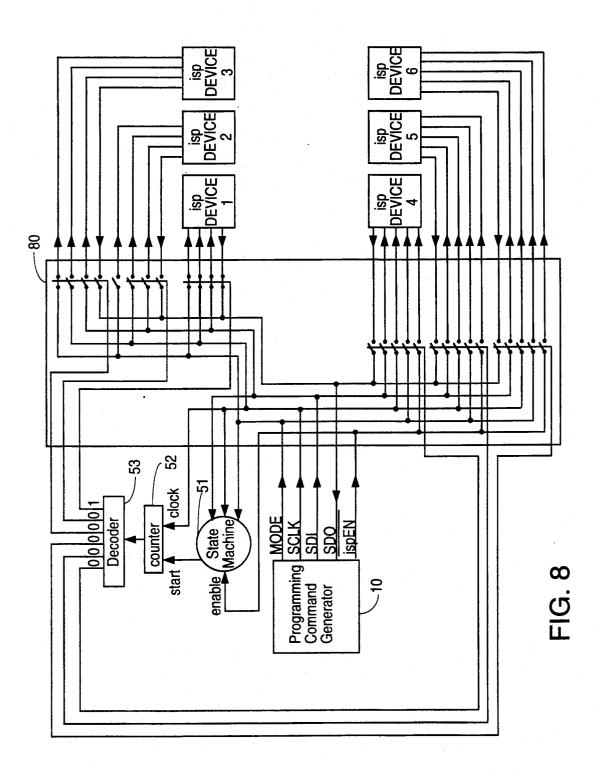

FIG. 8 illustrates a block diagram of an embodiment of the invention which includes a state machine-controlled switch matrix.

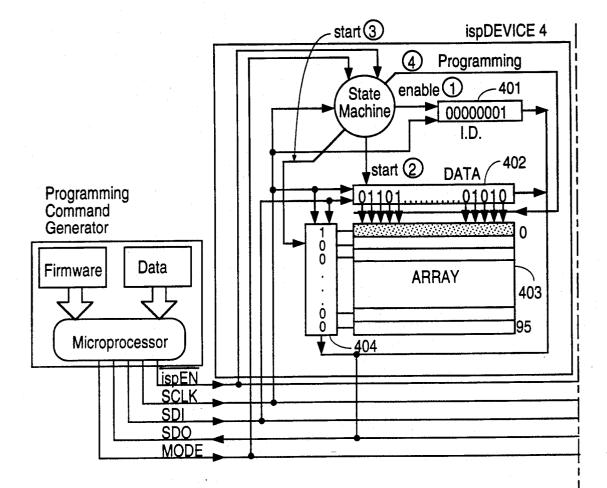

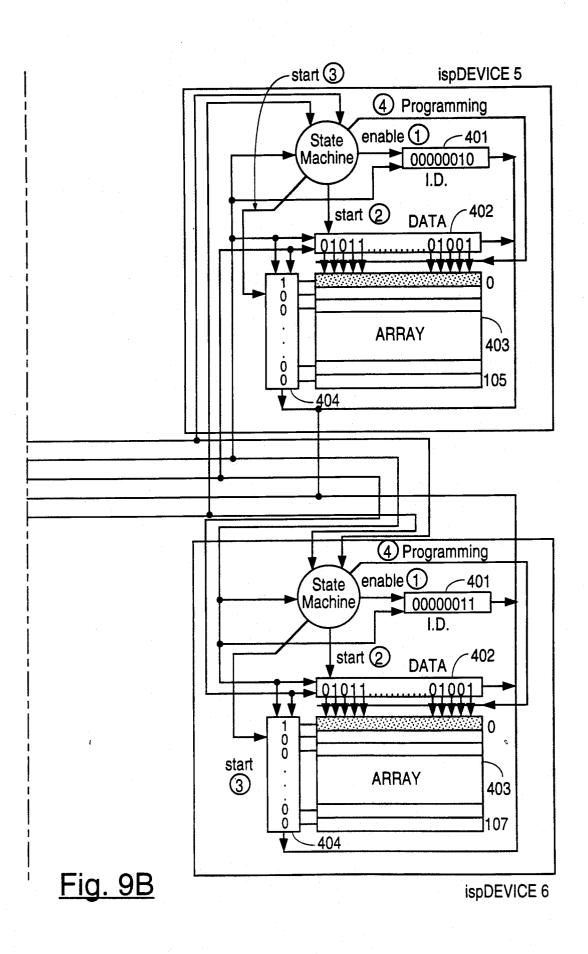

FIGS. 9, 9A and 9B illustrate a block diagram of an embodiment of the invention which does not include a device selector.

#### DESCRIPTION OF THE INVENTION

This invention will be described by reference to two types of ISP logic devices, both of which are manufactured by the assignee of this application, Lattice Semi-

The first of these devices is the ispGAL22V10, which has four programming pins: Mode, SCLK (Serial Clock), SDI (Serial Data In), and SDO (Serial Data Out). The device is placed in the programming mode by asserting the Mode signal high. Thereafter, the programming operation is controlled by the Mode and SDI pins. The structure and operation of this device are outlined below and are fully described in the isp-GAL22V10 Programmer's Guide, available from Lattice Semiconductor Corporation, which is incorporated herein by reference.

The second device is the Lattice ispLSI. This device is programmed by using five pins, designated: ispEN(isp Enable), Mode, SCLK, SCI and SCO. This device is 40 placed in the programming mode by asserting the ispEN pin low, which converts the other four pins from their normal functions to the programming mode. Thereafter, the programming is controlled by the Mode and SDI pins. The structure and operation of this device are outlined below and are fully described in the ispLSI Family Programming Spec., also available from Lattice Semiconductor Corporation and incorporated herein by reference.

This invention will be described with reference to six ispGAL22V10s and are therefore programmed using four pins, and ISP devices 4, 5 and 6 are ispLSIs and therefore are programmed using five pins.

FIG. 1 illustrates an embodiment in which the device generator 10 provides all of the signals necessary to program ISP devices 1-6 on lines designated Mode, SCLK, SDI, SDO and ispEN. Programming command generator 10 may, for example, be an IBM PC. A program suitable for programming command generator 10 is set forth at pp. 4-33 to 4-39 of the Lattice pLSI and ispLSI Data Book and Handbook (1992), available from Lattice Semiconductor Corp., which is incorporated herein by reference in its entirety. Programming com-65 mand generator 10 is connected to a demultiplexer 11 via a latch 12, which holds a 3-bit word designating which of ISP devices 1-6 is to be addressed. Demultiplexer 11 contains a decoder 13 having six outputs which control respective switches 14A-14F. The Mode output of programming command generator 10 connects to one side of switches 14A-14C which in turn run to ISP devices 1-3. The ispENoutput of programming command generator 10 is connected to one side of 5 switches 14D-14F which in turn run to devices 4-6.

If, for example, ISP device 1 is to be addressed, programming command generator 10 outputs a 001 to latch 12, and decoder 13 generates an output closing switch 14A, which connects the Mode line to ISP device 1. 10 When the programming of ISP device 1 has been completed, switch 14A is opened. If ISP device 4 is to be addressed, programming command generator 10 outputs a 100 to latch 12, and decoder 13 generates an output closing switch 14D, which connects the ispEN 15 line to ISP device 4. When the programming of ISP device 4 has been completed, switch 14D is opened. Program command generator cannot communicate with those of ISP devices 1–6 which correspond to any of switches 14A-14F that are open, and thus they do 20 not recognize the programming command.

The structure and operation of ISP devices 1-3 will be illustrated by reference to FIGS. 2 and 3. FIG. 3 illustrates a block diagram of the internal interface to the ISP pins and the functional units involved in the 25 programming operation. The programming operation is controlled by an instruction-based state machine 200 which is illustrated in FIG. 2. State machine 200 includes three states 201, 202 and 203, corresponding respectively to the idle, shift and execute states. Timing 30 of state machine 200 is provided by the clock signal on the SCLK pin. The state of state machine 200 is determined by the signals on the Mode and SDI pins, and every state change is effective at the next clock pulse after a change in the Mode and SDI inputs. When the 35 ISP device is functioning, state machine 200 stays locked in the idle state 201, which is unlocked when a high logic signal is received at the mode pin.

During the in-system programming mode, idle state 201 can be entered at any time from any state after one 40 clock pulse by bringing the signal on the Mode pin to a logic high and the signal on the SDI pin to a logic low. A transition from the idle state 201 to the shift state 202, from the shift state to the execute state 203, or from the execute state 203 back to the shift state 202 can be ac-45 complished by bringing both the Mode and the SDI pins to a logic high. When the Mode pin is at a logic low, the SDI pin is a data input pin, and the current state is held.

When the idle state 201 is entered, an 8-bit identifica- 50 tion is automatically loaded into an ID register 301. The 8-bit identification specifies such parametric values as the number of logic blocks on the chip, the number of I/O pins available, etc. and is "hard wired" into the device. Then the Mode pin goes to a logic low, and 55 seven clock pulses are applied to the SCLK pin to shift the identification in ID register 301 out the SDO pin to programming command generator 10 (the least significant bit of the identification already appears on the SDO pin). If programming command generator 10 rec- 60 ognizes the identification, communication is established with the ISP device.

As mentioned above, the shift state 202 is entered from the idle state 201 by bringing both the Mode and the SDI pins to a logic high. In the shift state 202, a 5-bit 65 command is shifted serially into the ISP device via the SDI line. The command may be to erase data in the ISP device, send programming data to the ISP device, pro-

gram the ISP device according to the data sent, extract programming data from the ISP device, or test the ISP device. Execution of the command is effected by bringing state machine 200 to the execute state 203, which is entered from the shift state 202 by bringing both the Mode and SDI pins to a logic high. Using 5-bit commands, 32 commands can be defined. The commands for device 4 are shown in Appendix A.

In the execute state 203, the command stored in the ISP device is executed. If the instruction is to load programming data into a data register 302 (i.e., the command "DATASHFT"), for example, the appropriate number of bits are shifted into data register 302 from the SDI pin after the Mode pin goes to a logic low, while the same number of bits in data register 302 are shifted out the SDO pin back to programming command generator 10. After the programming data have been shifted into register 302, a 5-bit command is issued to the ISP device by programming command generator 10 to transfer the programming data to row address 00 in a memory array 303. Array 303 contains a number of memory locations which correspond to programmable connections in the ISP device. After the data have been programmed to address 00, new programming data are sequentially shifted into register 302 and transferred to row address 01 of array 303. This process continues until all of addresses 00 through 44 are filled. Next, state machine 200 is stepped back to the command state 202 and the command to program the ISP device according to the data stored in array 303 is issued by programming command generator 10. The structure of ISP device 4 is illustrated in FIG. 4. State machine 400 is substantially identical to state machine 200 shown in FIG. 2. State machine 400 is activated when the ispENis driven low, and its transitions from one state to another are controlled by the Mode and SDI pins. Initially state machine 400 is instructed to load into an ID register 401 an 8-bit identification which is then shifted out via the SDO line to programming command generator 10. If programming command generator 10 recognizes the identification, communication is established with ISP device 4. Programming command generator 10 then commands state machine 400 to shift the programming data into a data register 402 via the SDI line. State machine 400 is then commanded to shift row selection data into a row register 404. In FIG. 4, row 0 is selected. The programming data are then transferred from data register 402 to row 0 in a programmable array 403. This process is repeated until all of rows 0 through 107 are filled with programming data. The programmable connections in ISP device 4 are then programmed in accordance with the data stored in array 403.

Referring again to FIG. 1, it will be noticed that the SCLK, SDI and SDO outputs of programming command generator 10 are connected in common to ISP devices 1-3, while the Mode output is connected to ISP devices 1-3 via demultiplexer 11. The Mode, SCLK, SDI and SDO outputs of programming command generator 10 are connected in common to ISP devices 4-6, while the ispENoutput is connected to ISP devices 4-6 via demultiplexer 11. As noted above, the respective state machines in ISP devices 1-3 are activated via the Mode pin, and the respective state machines in ISP devices 4-6 are activated via the ispENpin.

In the embodiment of FIG. 5, a state machine-controlled demultiplexer 50 is connected between programming command generator 10 and ISP devices 1-6. State machine-controlled demultiplexer 50 contains a state machine 51, a counter 52, a decoder 53 and switches 54A-54F. The ispENoutput of programming command generator 10 is connected to an input of state machine 50 and to one side of switches 54D-54F. The Mode output of programming command generator 10 is con- 5 nected to another input of state machine 50 and to one side of switches 54A-54C. The SDI output of programming command generator 50 is connected to another input of state machine 50. Clock pulses are provided to state machine 50 and counter 52 via the SCLK output of 10 is brought to a logic high and state machine 51 moves to programming command generator 10.

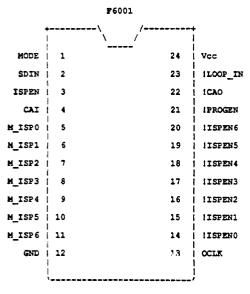

State machine 51 and counter 52 may advantageously reside in a Lattice GAL6001, the programming and structure of which are described in Appendix B and at pp. 2-147 to 2-161 of the Lattice GAL Data Book 15 (1992), available from Lattice Semiconductor Corporation and incorporated herein by reference. The control signals for state machine 51 are Mode and SDI. Each GAL6001 device can support 7, ISP devices, since it includes a 3-bit counter. The 3-bit counters of several 20 GAL6001 devices may be cascaded together to support as many ISP devices as required, as illustrated on page 17 of Appendix B.

FIG. 6 illustrates a flow chart for state machine 51, which includes fourteen "states". Movement from one 25 state to the next is controlled by the output of the SDI and Mode lines, and occurs with the clock pulses on the SCLK line. Since the SDI line is connected in common to state machine 51 as well as ISP devices 1-6, it is important to avoid issuing instructions to state machine 30 51 that would prompt any unwanted actions to be taken by ISP devices 1-6. This concern is accommodated by using the "no operation" command "00000" as a "wakeup" command for state machine 51 (see Appendix A).

State machine 51 is activated by bringing the ispEN 35 line to a logic low, which places state machine 51 in state 0. The SDI and Mode lines are then brought to a logic high to move state machine 51 to state 1. This moves state machines 200 in ISP devices 103 and state machines 400 in ISP devices 4-6 to the "shift" state 202 40 (see FIG. 2). Thereafter, the SDI line is brought to a logic low for five consecutive clock pulses, bringing state machine 51 to state 6. ISP devices 1-6 interpret this as a "no operation" command 00000 while it serves as a wake-up" command for state machine 51.

The SDI and Mode lines are then brought to a logic high, bringing state machine 51 to state 7 and the state machines in ISP devices 1-6 to the "execute" state 203. When the SDI and Mode lines are both brought low, state machine 51 moves to state 8, while the state ma- 50 chines in ISP devices 1-6 execute the command. Since the command was "no operation" however no action is taken as a result of this command. The SDI line is then brought high and the Mode line is brought low, moving state machine 51 to state 9, and moving the state ma- 55 chines in ISP devices 1-6 from the "execute" state to the "idle" state. This completes the "wake-up" cycle for state machine 51, and results in the state machines in ISP devices 1-6 being in the "idle" state. These state machines will remain in the "idle" state so long as a 60 logic high does not appear on both the SDI and Mode lines.

The SDI and Mode lines are then both brought low, which resets counter 52 to zero. If the SDI and Mode lines remain low, state machine 51 proceeds to state 11. 65 The Mode line is then brought to a logic high, and remains in this condition as programming command generator 10 delivers a number of clock pulses represen-

tative of the ISP device to be selected. Each of these clock pulses causes counter 52 to advance one binary word. For example, if ISP device 5 is to be selected, five clock pulses would be delivered to counter 52 leaving it in a "101" state. The binary word in counter 52 is reflected at all times in decoder 53, so that switches 54A, 54B, etc. are closed in succession as counter 52 steps forward. When the desired number is reached (i.e., the desired one of switches 54A-54F is closed) the SDI line state 12. This terminates the clocking of counter 52 and leaves the desired switch closed.

States 13 and 14 are optional features that are not required for programming the ISP devices. The use of state 13 allows the user to receive a visual reading of which ISP device has been selected. When state machine 51 arrives at state 11, the Mode line is brought low, moving state machine 51 to state 13. The SDI line is then brought low and the Mode line is brought high and counter 52 is pulsed as described above. At the same time, the user is given a visual indication of which device has been selected. If the visual indication indicates that the correct device has been selected, both the SDI and Mode lines are brought high, causing the device to be enabled. Otherwise, if the Mode line is brought low, the device remains disabled.

State 14 is used in the situation where more than seven ISP devices are being programmed. As noted above, since counter 52 is a 3-bit counter this requires that at least one additional counter be cascaded with counter 52. In this configuration, when state machine 51 reaches a "111" the next clock pulse would drive the second counter to a "001". Each time a counter fills up, a "1" appears on the line connecting it with the next cascaded counter, and in the case of the last counter on the SDO line. When state machine 51 is moved to state 14, programming command generator 10 counts the pulses delivered on the SCLK line while monitoring the SDO line. When a "1" appears on the SDO line, programming command generator 10 can determine the number of counters cascaded by dividing the number of pulses delivered by seven. This enables the user to determine how many counters are cascaded together.

FIG. 7 shows an embodiment including switch ma-45 trixes 70 and 71. Latch 12 and decoder 13 are identical to the similarly numbered components shown in FIG. 1. Three outputs of decoder 12 control switch groups in matrix 70, which connect the Mode, SCLK, SDI and SDO outputs to ISP devices 1-3, respectively. The remaining three outputs of decoder 13 control switch groups in switch matrix 71, and connect the Mode, SCLK, SDI, SDO and ispENto ISP devices 4-6, respectively. As shown in FIG. 7, if the numeral 001 is delivered to latch 12, decoder 13 will close the switches connecting programming command generator 10 to ISP device 1. ISP Device 1 is then programmed as described above. Similarly, ISP devices 2-6 may be connected to programming command generator 10 and programmed.

FIG. 8 illustrates yet another embodiment which includes a state machine controlled switch matrix 80. State machine 51, counter 52 and decoder 53 are identical to the similarly numbered components shown in FIG. 5. These devices function together in the same manner described above in connection with FIG. 5 to close the desired group of switches in switch matrix 80, thereby connecting the required output lines from programming command generator 10 to a desired one of ISP devices 1-6.

FIG. 9 illustrates another embodiment which omits the device selector. ISP devices 4-6 are shown connected to program command generator 10. Each of ISP devices 4-6 has a different 8-bit identification, the identification being "0000001" for ISP device 4, "00000010" 5 for ISP device 5, and "00000011" for ISP device 6. Program command generator 10 drives the ispENlow, which results in the identification being loaded into the ID register 401 in each device.

Suppose ISP device 4 is to be programmed. Program-<sup>10</sup> ming command generator 10 shifts the identification of ISP device 4 ("00000001") into the ID register 401 in each of the devices. A comparison means in each device compares the identification in ID register 401 with the permanently stored identification in the device, and as a <sup>15</sup> result a match occurs only in ISP device 4. Therefore, communication is established only with ISP device 4 for data transfer from programming command generator 10, and ISP devices 5 and 6 are not activated for programming.<sup>20</sup>

Programming command generator 10 then shifts the programming data into the data register 402 and the row address information into row register 404 of ISP device 4. Programming command generator 10 then drives the Mode pin high and the SDI pin low and pulses the SCLK pin. This loads the internally stored identification of each device into its respective ID register 401.

This process is then repeated except that the identification for ISP device 5 is shifted out of programming command generator 10 and programming data for one row are entered into ISP device 5. Similarly, the identification for ISP device 6 is entered into ID registers 401, and the programming data for one row are entered into ISP device 6. Programming command generator 10 then drives the Mode pin high and the SDI pin low and pulses the SCLK pin. This loads the internally stored identification of each device into its respective register 401. Programming command generator 10 then sends out the programming command. Since at the end of each entry of a row of programming data the internally stored identification is automatically loaded into the

corresponding ID register 401, when the programming command is issued there is a match between the identification stored in ID register 401 and the permanently stored identification in each of ISP devices 4–6, and the command is executed for the data held in register 402 in each device. This process is continued until the respective programmable arrays 403 in devices 4–6 are completely programmed.

The embodiments described above have various advantages and disadvantages. The system which includes a demultiplexer (FIG. 1) uses a minimal traces on a circuit board and can support any mix of ISP devices. However, it does require the addition of a demultiplexer and additional trace circuitry is required to connect programming command generator 10 with latch 12.

The system which includes a state machine-controlled multiplexor (FIG. 5) requires minimal traces on a circuit board and can also support any mix of ISP devices. No additional traces are required to connect programming command generator 10 to state machinecontrolled demultiplexer 50, and the programming time is minimized by programming all of the ISP devices simultaneously. However, this system requires a fairly complex IC for the state machine-controlled multiplexor.

The embodiments which include a switch matrix (FIGS. 7 and 8) require a greater number of traces on a printed circuit board.

The embodiment shown in FIG. 9 requires minimal traces on a circuit board, and no additional component such as a multiplexor is required. Moreover, programming time is minimized because all of the ISP devices can be programmed simultaneously. However, none of the ISP devices may have exactly the same identity.

The foregoing embodiments are intended to be illustrative only and not limiting. Additional embodiments will be apparent to those skilled in the art. For example, the embodiments shown in FIG. 9 can be combined with the other embodiments to program a group of ISP devices. All such additional embodiments are included within the broad scope of this invention, which is defined in the following claims.

#### 45

25

#### <u>APPENDIX A</u>

|    |          | <u>Operation</u>                                                                                                           | <u>Code</u> |

|----|----------|----------------------------------------------------------------------------------------------------------------------------|-------------|

| ο. | NOP      | No operation                                                                                                               | 00000       |

| 1. | ADDSHFT  | Address register shift                                                                                                     | 00001       |

| 2. | DATASHFT | Data register shift                                                                                                        | 00010       |

| 3. | GBE      | Global bulk erase<br>Erase pia, array, architecture and<br>security cells                                                  | 00011       |

| 4. | PIABE    | PIA bulk erase<br>Erase pia cells                                                                                          | 00100       |

| 5. | ARRBE    | Array bulk erase<br>Erase array cells                                                                                      | 00101       |

| 6. | ARCHBE   | Architecture bulk erase<br>Erase architecture cells                                                                        | 00110       |

| 7. | PROGEVEN | Program even columns<br>Program even columns of array,<br>pia and architecture cells at<br>the rows selected by Address SR | 00111       |

| Э. |

|----|

|    |

|    |

|     |            | 9                                                                                                                                                                           |              |

|-----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 8.  | PROGODD    | Program odd columns<br>Program odd columns of array,<br>pia and architecture cells at<br>the rows selected by Address SR                                                    | 01000        |

| 9.  | SFPRG      | Program security cell                                                                                                                                                       | 01001        |

| 10. | VERIFYEVEN | Verify even columns programmed<br>cells<br>Verify even columns of array, pia<br>and architecture programmed cells.<br>Only one row can be selected for<br>each verification | 01010        |

| 11. | VERIFYODD  | Verify odd columns programmed<br>cells<br>Verify odd columns of array, pia<br>and architecture programmed cells.<br>Only one row can be selected for ea<br>verification     | 01011<br>Ach |

| 12. | GLCPRELD   | Preload GLB registers                                                                                                                                                       | 01100        |

| 13. | IOPRELD    | Preload I/O Cell registers                                                                                                                                                  | 01101        |

| 14. | FLOWTHRU   | Flow through<br>SDI flow through to SDO                                                                                                                                     | 01110        |

| 15. | PROGESR    | Program ESR<br>Address SR is automatically<br>cleared to 0                                                                                                                  | 01111        |

| 16. | ERAALL     | Erase all<br>Erase pia, array, architecture,<br>ES and security cells                                                                                                       | 10000        |

| 17. | VERESR     | Verify ESR<br>Address SR is automatically<br>cleared to 0                                                                                                                   | 10001        |

| 18. | VEREVENH   | Verify even columns erased cells<br>Verify even columns pia, array and<br>architecture erased cells. Only<br>one row can be selected for each<br>verification               | 10010        |

| 19. | VERODDH    | Verify odd columns erased cells<br>Verify odd columns pia, array and<br>architecture erased cells. Only<br>one row can be selected for each<br>verification                 | 10011        |

| 20. | NOP        | No operation                                                                                                                                                                | 10100        |

| 31. | INIT       | Initialize                                                                                                                                                                  | 11111        |

|     |            | APPENDIX B                                                                                                                                                                  |              |

#### APPENDIX B

#### Programming and Connection of Lattice GAL 6001

## Pages 1 to 6:

ABEL high level language design file to perform the logic function represented by the state machine shown in Fig. 6.

### Pages 7 to 11:

ABEL document file generated by ABEL compiler available from Data I/O Corporation.

## Pages 12 to 16:

JEDEC file used to implement the above-noted logic function.

#### <u>Page 17:</u>

Connections required to cascade two GAL 6001 devices together to support more than seven ISP devices.

10

DEVICE 'f6001';

11

" control inputs

| OCLK    | pin 13; |

|---------|---------|

| MODE    | pin 1 ; |

| SDIN    | pin 2 ; |

| ISPEN   | pin 3 ; |

| CAI     | pin 4 ; |

| M_ISP0  | pin 5;  |

| M_ISP1  | pin 6;  |

| M_ISP2  | pin 7;  |

| M_ISP3  | pin 8;  |

| M_ISP4  | pin 9;  |

| M_ISP5  | pin 10; |

| M_ISP6  | pin 11; |

| LOOP_IN | pin 23; |

outputs

| ISPENO | pin 14; |

|--------|---------|

| ISPEN1 | pin 15; |

| ISPEN2 | pin 16; |

| ISPEN3 | pin 17; |

| ISPEN4 | pin 18; |

| ISPEN5 | pin 19; |

| ISPEN6 | pin 20; |

| PROGEN | pin 21; |

| CAO    | pin 22; |

### state registers

| STO node 26     |   |

|-----------------|---|

| ST1 node 27     | ; |

| ST2 node 28     | ; |

| ST3 node 29     | ; |

| T_REG0 node 31; |   |

| T_REG1 node 32; |   |

| T_REG2 node 33; |   |

| SHFT node 30;   |   |

| ISPENO, ISPEN1, ISPEN2, ISPEN3 | ISTYPE | 'COM';                |

|--------------------------------|--------|-----------------------|

| ISPEN4, ISPEN5, ISPEN6         | ISTYPE | 'COM';                |

| CAO                            | ISTYPE | 'REG G, INVERT, POS'; |

| T_REG0, T_REG1, T_REG2         | ISTYPE | 'REG G, BUFFER, POS'; |

| PROGEN                         | ISTYPE | 'REG_G, INVERT, NEG'; |

" Simulation Symbol Definitions

```

H = 1 ;

L = 0 ;

C = .C.;

X = .X.;

Z = .2.;

* State Bit Assignments

PSTATES = [ST3..ST0];

* Device Enable Counter

DCOUNT = [T_REG2,T_REG1,T_REG0];

EQUATIONS

PSTATES.CLK=OCLK;

DCOUNT.CLK=OCLK;

DCOUNT.CLK=OCLK;

CAO.CLK=OCLK;

PROGEN.CLK=OCLK;

LOOP_IN.OE = 0;

ISPEN0 = (M_ISP0) ;

ISPEN0.OE = (!ISPEN & !T_REG2 & !T_REG1 & T_REG0 & !PROGEN.FB);

```

13 ISPEN1 = (M\_ISP1) ISPENI.OE = (!ISPEN & !T\_REG2 & T\_REG1 & !T\_REG0 & !PROGEN.FB); ISPEN2 = (M\_ISP2) ISPEN2.OE = (!ISPEN & !T\_REG2 & T\_REG1 & T\_REG0 & !PROGEN.FB); ISPEN3 = (M\_ISP3) ISPEN3.OE = (!ISPEN & T\_REG2 & !T\_REG1 & !T\_REG0 & !PROGEN.FB);  $ISPEN4 = (M_ISP4)$ ISPEN4.OE = (!ISPEN & T REG2 & !T REG1 & T REG0 & !PROGEN.FB); ISPEN5 = (M ISP5)ISPEN5.OE = (!ISPEN & T\_REG2 & T\_REG1 & !T\_REG0 & !PROGEN.FB);  $ISPEN6 = (M_ISP6)$ ISPEN6 = (M\_ISP6) ; ISPEN6.OE = (!ISPEN & T\_REG2 & T\_REG1 & T\_REG0 & !PROGEN.FB); " Internal Counter Bit Equations T\_REG0.D = !T\_REG0 & !(PSTATES==10) & CAO & !ISPEN & !SHFT; T\_REG0.CE = ((PSTATES==11) & !MODE & SDIN & !CAI # (PSTATES==10) # ISPEN); T\_REG1.D = !T\_REG1 & !(PSTATES==10) & CAO & !ISPEN & !SHFT; T\_REG1.CE = ((PSTATES==11) & !MODE & SDIN & !CAI & T\_REGO Ŧ (PSTATES==10) # ISPEN); T\_REG2.D = !T\_REG2 & !(PSTATES==10) & CAO & !ISPEN & !SHFT; T\_REG2.CE = ((PSTATES==11) & !MODE & SDIN & !CAI & T REGO & T REG1 # (PSTATES==10) # ISPEN); CAO.AR = ISPEN; " State Machine Definition For isp MUX states STATE\_DIAGRAM PSTATES STATE 0: if (MODE & SDIN & !ISPEN) then 1; else 0; STATE 1: if (MODE & !SDIN & !ISPEN) then 2; else 0 ; STATE 2: if (MODE & !SDIN & !ISPEN) then 3; Alse 0; STATE 3: if (MODE & !SDIN & !ISPEN) then 4 ; else 0; STATE 4: if (MODE & !SDIN & !ISPEN) then 5; 0; else STATE 5: if (MODE & !SDIN & !ISPEN) then 6; 0; else STATE 6: if (MODE & SDIN & !ISPEN) then 7; 0; else STATE 7: if (!MODE & !SDIN & !ISPEN) then 8; else 0;

15 STATE 8: if (MODE & !SDIN 9; & !ISPEN) then else 0; STATE 9: PROGEN.CE=1; CAO.CE=1; DCOUNT.CE=1; if (!MODE & !SDIN £ !ISPEN) then 10 with CAO.D=0; DCOUNT.D=0; PROGEN.D=0; else 0; SHFT.CE=1; STATE 10: if (IMODE & ISDIN & !ISPEN) then 11: else if (!MODE & SDIN

& !ISPEN) then 14 with SHFT.D=1; else 0; STATE 11: CAO.CE=(DCOUNT==7) & !MODE & SDIN & !ISPEN; SHFT.CE=1; if (!MODE & SDIN & IISPEN) then 11 with CAO.D=(DCOUNT==7); else if (MODE & !SDIN & !ISPEN) then 13 with SHFT.D=1; else if (!MODE & !SDIN & !ISPEN) then 13 with SHFT.D=1; else if (MODE & SDIN & !ISPEN) then 12; STATE 12: PROGEN.CE=1; GOTO 0 with PROGEN.D=CAO; STATE 13: CAO.CE=(!MODE & SDIN & !ISPEN); PROGEN :1; DCOUNT.CE=(!MODE & SDIN & !ISPEN); SHFT.CE=1; if (!MODE & SDIN & !ISPEN) then 13 with CAO.D=!T REGO.Q & SHFT; T\_REG0.D=T\_REG1.Q & SHFT; T\_REG1.D=T\_REG2.Q & SHFT; T\_REG2.D=LOOP\_IN & SHFT; SHFT.D=1; else if (MODE & SDIN & !ISPEN) then 0 with PROGEN.D=1; SHFT.D=0; else 0 with PROGEN.D=0; SHFT.D=0; STATE 14: CAO.CE=(!MODE & SDIN & !ISPEN); DCOUNT.CE=(!MODE & SDIN & !ISPEN); SHFT.CE=1; if (!MODE & SDIN & !ISPEN) then 14 with CAO.D=!T\_REG0.Q & SHFT; T\_REG0.D=T\_REG1.Q & SHFT; T\_REG1.D=T\_REG2.Q & SHFT; T\_REG2.D=!CAI & SHFT; 0 with SHFT.D=0; else . TEST\_VECTORS

([OCLK, ISPEN, MODE, SDIN, CAI, LOOP\_IN, M\_ISP0, M\_ISP1, M\_ISP2, M\_ISP3, M\_ISP4, M\_ISP5, M\_ISP [PSTATES, DCOUNT, CAO, ISPENO, ISPENI, ISPEN2, ISPEN3, ISPEN4, ISPEN5, ISPEN ISPEN0 ENABLE CHECK

|   |                                                                                         |                                          |                                                    |                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               | . /                                          |                                          |                                              |                                          |                                              |                                         |                                                                                 |                                                                                 |                                                                                    |                                              |                                                             |                                                                    |                                                                                 |                                            | TO                                     |                                                                    |                                                                              |                                                                               |                                                          |                                         |

|---|-----------------------------------------------------------------------------------------|------------------------------------------|----------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------|------------------------------------------|----------------------------------------------|------------------------------------------|----------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------|----------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------|

|   |                                                                                         | 000000000000000000000000000000000000000  | 101000101111111010                                 | 100011111000001000,                                | 000000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 000000000000000000000000000000000000000       | 000000000000000000000000000000000000000      | 000000000000000000000000000000000000000  | 000000000000000000000000000000000000000      | 000000000000000000000000000000000000000  | 000000000000000000000000000000000000000      | 000000000000000000000000000000000000000 | 01<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>01<br>0 | ->-<[[]]<br>->->[]]<br>->->->->->->->->->->->->->->->->->->-                    | 7,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                             | 0,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,      | 日日日日日日日日日日日日日日日日日日日日日日日日日日日日日日日日日日日日日日                      | 222222211111111111                                                 | 22222222222222222222                                                            | 2222222222222222222222                     | 222222222222222222222                  | 22222222222222222222                                               | 2222222222222222222222                                                       | 222222222222222222222                                                         | EBEELLILLLLLLLLLLLLLLLLLLLLLLLLLLLLLLLL                  |                                         |

|   | 0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,                                                | 0,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,  | 0,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,            | 1,<br>1,<br>1,<br>1,<br>1,<br>1,<br>1,<br>1,<br>1, | 0,,00,00,00,00,00,00,00,00,00,00,00,00,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0, 0, 0, 0, 0, 0, 0,                          | 0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,       | 0,<br>0,<br>0,<br>0,<br>0,               | 0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,       | 0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,   | 0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,       | 0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,  | 0]<br>0]<br>0]<br>0]<br>0]<br>0]<br>0]                                          | ->[]<br>->[]<br>->[]<br>->[]<br>->[]<br>->[]                                    | 11,<br>11,<br>11,<br>11,<br>11,<br>11,<br>[11,                                     | 1,<br>2,<br>3,<br>4,<br>5,<br>6,<br>7,<br>0, | E,,<br>EE,,<br>EE,,<br>EE,,<br>EE,,<br>EE,,<br>EE,,<br>EE,, | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,                             | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,                                          | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,     | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z, | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,                             | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,                                       | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,                                        | <pre>E]; E]; E]; E]; E]; E]; E]; E];</pre>               | 7                                       |

|   |                                                                                         | 0,,00,00,00,00,00,00,00,00,00,00,00,00,  | 0,<br>1,<br>1,<br>1,<br>1,<br>1,<br>1,<br>1,<br>0, | 1,<br>1,<br>0,<br>0,<br>0,<br>0,<br>1,<br>0,<br>0, | 0,,00,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,000,0000 | 0,,,0,,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0      | 0,,00,00,00,00,00,00,00,00,00,00,00,00,      | 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0 | 0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0, | 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0 | 0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0, | 0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,  |                                                                                 | -><br>-><br>-><br>-><br>-><br>-><br>-><br>-><br>-><br>-><br>-><br>-><br>-><br>- | [ 2,<br>[ 3,<br>[ 4,<br>[ 5,<br>[ 7,                                               | 0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,       | L, L, L, L, L, L, L,                                        | Z,,<br>Z,,<br>Z,,<br>Z,,<br>Z,,<br>Z,,<br>Z,,<br>Z,,<br>Z,,<br>Z,, | 2,<br>2,<br>2,<br>2,<br>2,<br>2,<br>2,<br>2,<br>2,<br>2,<br>2,<br>2,<br>2,<br>2 | Z,,<br>Z,Z,Z,Z,Z,Z,Z,Z,Z,Z,Z,Z,Z,Z,Z,Z,Z,Z | Z, , , , , , , , , , , , , , , , , , , | Z,,<br>Z,,<br>Z,,<br>Z,,<br>Z,,<br>Z,,<br>Z,,<br>Z,,<br>Z,,<br>Z,, | Z,,<br>Z,,<br>Z,,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z | 2,<br>2,<br>2,<br>2,<br>2,<br>2,<br>2,<br>2,<br>,<br>2,<br>,<br>2,<br>,<br>2, | H]<br>H]<br>H]<br>H]<br>H]<br>H]<br>H]                   | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

|   |                                                                                         |                                          | 0,000000101111,                                    | 1111111111000,                                     | ·····                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 000000000000000000000000000000000000000       |                                              | 000000000000000000000000000000000000000  | 000000000000000000000000000000000000000      | 0,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,  | 000000000000000000000000000000000000000      | 000000000000000000000000000000000000000 |                                                                                 | -><br>-><br>-><br>-><br>-><br>-><br>-><br>-><br>-><br>-><br>-><br>-><br>-><br>- | 11,<br>11,<br>11,<br>11,<br>11,<br>11,<br>11,<br>12,<br>0,<br>1,<br>2,<br>3,<br>4, | 1,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,      |                                                             | Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z                              | 2,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                         | Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z      | Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z  | Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z Z                              | 2,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                      | 2,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                        | H]<br>H]<br>H]<br>H]<br>H]<br>H]<br>L]<br>L]<br>L]<br>L] | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; |

| - | [ C,<br>[ C,<br>[ C,<br>[ C,<br>[ C,<br>] DIS<br>[ 0,                                   | 0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>ABL  | 1,<br>1,<br>1,<br>0,<br>1,<br>0,<br>E I,           | 0,<br>0,<br>1,<br>0,<br>0,<br>SP 1                 | 0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0,<br>0,<br>0,<br>0,<br>0,<br>0,              | 0,<br>0,<br>0,<br>0,<br>0,                   | 0,<br>0,<br>0,<br>0,<br>0,<br>0,         | 0,<br>0,<br>0,<br>0,<br>0,<br>0,             | 0,<br>0,<br>0,<br>0,<br>0,<br>0,         | 0,<br>0,<br>0,<br>0,<br>0,<br>0,             | 0,<br>0,<br>0,<br>0,<br>0,              | 0]<br>0]<br>0]<br>0]<br>0]                                                      | -> <br> -> <br> ->[<br> ->[<br> ->[                                             | 5,<br>6,<br>7,<br>8,<br>9,<br>10,                                                  | 7,<br>7,<br>7,<br>7,<br>7,<br>7,<br>0,       | HHHHHHHHHHHHHHHH                                            | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,                                   | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,                                                | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,           | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,       | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,                                   | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,                                             | L,<br>L,<br>L,<br>L,<br>Z,                                                    | L].<br>L].<br>L].<br>L].<br>H].                          | ;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; |

|   | 0,<br>CHE<br>C,<br>C,<br>C,<br>C,<br>C,<br>C,<br>C,<br>C,<br>C,<br>C,<br>C,<br>C,<br>C, | CK :<br>0,<br>0,<br>0,<br>0,<br>0,<br>0, | SER<br>1,<br>1,<br>1,<br>1,<br>1,<br>1,<br>0,      | IAL<br>1,<br>0,<br>0,<br>0,<br>0,<br>1,<br>0,      | SH<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IFT<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0, | OU<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,<br>0, | F<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,    | OR :<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,     | NUM<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,  | BER<br>0,<br>0,<br>0,<br>0,<br>0,<br>0,      | OF<br>0,<br>0,<br>0,<br>0,<br>0,        | MC<br>0]<br>0]<br>0]<br>0]<br>0]<br>0]                                          | IX<br>->[<br>->[<br>->[<br>->[<br>->[<br>->[                                    | 1,<br>2,<br>3,<br>4,<br>5,<br>6,<br>7,<br>8,                                       | 0,,0,,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,0,     | E E E E E E E E E E E E E E E E E E E                       | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,                             | Z,,<br>ZZ,,<br>ZZ,,<br>ZZ,<br>ZZ,                                               | 2,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,     | Z,,<br>Z,,<br>Z,,<br>Z,,<br>Z,,<br>Z,, | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,                             | Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,<br>Z,                                       | Z,,,,,<br>Z,,,,,<br>Z,,,,,                                                    | H];<br>H];<br>H];<br>H];<br>H];<br>H];<br>H];            | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

19

|                     | 19                | 0,020,110                                | 20                          |

|---------------------|-------------------|------------------------------------------|-----------------------------|

|                     | 17                |                                          | 20                          |

| [C, 0, 0, 0]        | 0, 0, 0, 0, 0,    | $0, 0, 0, 0] \rightarrow [10, 0, H]$     | , Z, Z, Z, Z, Z, Z, Z, H);  |

| [ C, 0, 0, 1,       | 0, 0, 0, 0, 0, 0, | 0, 0, 0, 0  ->   14, 0, E                | , Z, Z, Z, Z, Z, Z, Z, H];  |

| [ C. 0. 0. 1.       | 0. 0. 0. 0. 0.    | $0, 0, 0, 01 \rightarrow [14, 0, 1]$     | , Z, Z, Z, Z, Z, Z, Z, H];  |

|                     |                   |                                          | , Z, Z, Z, Z, Z, Z, Z, H];  |

|                     |                   |                                          | , Z, Z, Z, Z, Z, Z, Z, H];  |

|                     |                   |                                          |                             |

|                     |                   |                                          | , Z, Z, Z, Z, Z, Z, Z, H];  |

|                     | SHIFT OUT FOR I   |                                          |                             |

| [0, 1, 1, 1]        | 0, 0, 0, 0, 0, 0, | $0, 0, 0, 0] \rightarrow [0, 0, H]$      | , Z, Z, Z, Z, Z, Z, H];     |

|                     |                   |                                          | , Z, Z, Z, Z, Z, Z, Z, H];  |

| [C, 0, 1, 0,        | 0, 0, 0, 0, 0,    | 0, 0, 0, 0]->[ 2, 0, H                   | , Z, Z, Z, Z, Z, Z, Z, H];  |

| [C, 0, 1, 0,        | 0, 0, 0, 0, 0,    | 0, 0, 0, 0]->[ 3, 0, H                   | , Z, Z, Z, Z, Z, Z, Z, H];  |

|                     |                   |                                          | , Z, Z, Z, Z, Z, Z, Z, H];  |

|                     |                   |                                          | , Z, Z, Z, Z, Z, Z, Z, H];  |

|                     |                   |                                          | , Z, Z, Z, Z, Z, Z, Z, H];  |

|                     |                   |                                          | , Z, Z, Z, Z, Z, Z, Z, H];  |

|                     |                   |                                          | , 2, 2, 2, 2, 2, 2, 2, H];  |

|                     |                   |                                          | , Z, Z, Z, Z, Z, Z, Z, H];  |

|                     |                   |                                          |                             |

|                     | 0, 0, 0, 0, 0, 0, | [0, 0, 0, 0] = 2[10, 0, B]               | , Z, Z, Z, Z, Z, Z, Z, H];  |

|                     |                   |                                          | , Z, Z, Z, Z, Z, Z, Z, H];  |

| [ C, O, O, O,       | 0,0,0, 0,         | $0, 0, 0, 0] \rightarrow [11, 1, B]$     | I, , Z, Z, Z, Z, Z, Z, H];  |

| $\{ C, 0, 0, 1, \}$ | 0, 0, 0, 0, 0, 0, | 0, 0, 0, 0]->[13, 1, E                   | I, Z, Z, Z, Z, Z, Z, Z, H); |

| [C, 0, 0, 1]        | 0, 1, 0, 0, 0,    | $0, 0, 0, 0] \rightarrow [13, 0, B]$     | I, Z, Z, Z, Z, Z, Z, Z, H]; |

| [C, 0, 0, 1]        | 0, 0, 0, 0, 0, 0, | 0, 0, 0, 0  ->  13, 4, 1                 | , Z, Z, Z, Z, Z, Z, Z, H];  |

| [ C, 0, 0, 1,       | 0, 0, 0, 0, 0,    | 0, 0, 0, 0                               | , Z, Z, Z, Z, Z, Z, Z, H];  |

| [ C. 0. 0. 1.       | 0.0.0.0.0.        | $0, 0, 0, 0 \rightarrow 13 1 T$          | , Z, Z, Z, Z, Z, Z, Z, H];  |

| ſ Ċ. 0, 1, 1,       | 0, 0, 0, 0, 0,    | 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0 | l, L, Z, Z, Z, Z, Z, Z, L]; |

| , -, -, +,          | -, , , , , , ,    |                                          |                             |

|                     |                   |                                          |                             |

•

.

end isphw60 ;

•

.

ABEL 4.20 - Device Utilization Chart

==== F6001 Programmed Logic =====

| ST3.D<br>ST3.C | <pre>= ( !MODE &amp; !SDIN &amp; !ISPEN &amp; ST0.Q &amp; ST1.Q &amp; ST2.Q &amp; !ST3.Q<br/>MODE &amp; !SDIN &amp; !ISPEN &amp; !ST0.Q &amp; !ST1.Q &amp; !ST2.Q &amp; ST3.Q<br/>!MODE &amp; !SDIN &amp; !ISPEN &amp; ST0.Q &amp; !ST1.Q &amp; !ST2.Q &amp; ST3.Q<br/>!MODE &amp; !SDIN &amp; !ISPEN &amp; !ST0.Q &amp; ST1.Q &amp; !ST2.Q &amp; ST3.Q<br/>!MODE &amp; SDIN &amp; !ISPEN &amp; !ST0.Q &amp; ST1.Q &amp; !ST2.Q &amp; ST3.Q<br/>!MODE &amp; SDIN &amp; !ISPEN &amp; !ST0.Q &amp; ST1.Q &amp; !ST2.Q &amp; ST3.Q<br/>!MODE &amp; SDIN &amp; !ISPEN &amp; !ST0.Q &amp; ST1.Q &amp; !ST2.Q &amp; ST3.Q<br/>!MODE &amp; SDIN &amp; !ISPEN &amp; !ST0.Q &amp; ST1.Q &amp; !ST2.Q &amp; ST3.Q<br/>!MODE &amp; SDIN &amp; !ISPEN &amp; ST0.Q &amp; ST1.Q &amp; ST2.Q &amp; ST3.Q<br/>!MODE &amp; SDIN &amp; !ISPEN &amp; ST0.Q &amp; ST1.Q &amp; ST2.Q &amp; ST3.Q<br/>!MODE &amp; SDIN &amp; !ISPEN &amp; ST0.Q &amp; ST1.Q &amp; ST2.Q &amp; ST3.Q<br/>!MODE &amp; SDIN &amp; !ISPEN &amp; ST0.Q &amp; ST1.Q &amp; ST2.Q &amp; ST3.Q<br/>!MODE &amp; !ISPEN &amp; ST0.Q &amp; ST1.Q &amp; !ST2.Q &amp; ST3.Q<br/>!SDIN &amp; !ISPEN &amp; ST0.Q &amp; ST1.Q &amp; ST3.Q );<br/>"ISTYPE 'BUFFER'<br/>= ( OCLK );        </pre> |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | <pre>= ( MODE &amp; SDIN &amp; !ISPEN &amp; !ST0.Q &amp; ST1.Q &amp; ST2.Q &amp; !ST3.Q<br/># MODE &amp; !SDIN &amp; !ISPEN &amp; !ST1.Q &amp; ST2.Q &amp; !ST3.Q<br/># !MODE &amp; SDIN &amp; !ISPEN &amp; !ST0.Q &amp; ST1.Q &amp; !ST2.Q &amp; ST3.Q<br/># MODE &amp; !SDIN &amp; !ISPEN &amp; ST0.Q &amp; ST1.Q &amp; !ST2.Q &amp; ST3.Q<br/># !MODE &amp; SDIN &amp; !ISPEN &amp; ST0.Q &amp; ST1.Q &amp; ST2.Q &amp; ST3.Q<br/># !MODE &amp; SDIN &amp; !ISPEN &amp; ST0.Q &amp; ST1.Q &amp; ST2.Q &amp; ST3.Q<br/># !MODE &amp; SDIN &amp; !ISPEN &amp; ST0.Q &amp; ST1.Q &amp; ST2.Q &amp; ST3.Q<br/># MODE &amp; SDIN &amp; !ISPEN &amp; ST0.Q &amp; ST1.Q &amp; ST2.Q &amp; ST3.Q<br/># MODE &amp; SDIN &amp; !ISPEN &amp; ST0.Q &amp; ST1.Q &amp; ST2.Q &amp; ST3.Q<br/># MODE &amp; 1ISPEN &amp; ST0.Q &amp; ST1.Q &amp; !ST2.Q &amp; ST3.Q<br/># !SDIN &amp; !ISPEN &amp; ST0.Q &amp; ST1.Q &amp; !ST2.Q &amp; ST3.Q );<br/>" ISTYPE 'BUFFER'</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ST2.C          | = ( OCLK );                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ST1.D<br>ST1.C | <pre>= ( MODE &amp; !SDIN &amp; !ISPEN &amp; !ST0.Q &amp; ST1.Q &amp; !ST2.Q &amp; !ST3.Q</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5,329,179                                                                                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21 22                                                                                                                                                                                                                                 |

| <pre>ST0.D = ( MODE &amp; !SDIN &amp; !ISPEN &amp; !ST0.Q &amp; !ST1.Q &amp; ST2.Q &amp; !ST3.Q</pre>                                                                                                                                 |

| STO.C = (OCLK);                                                                                                                                                                                                                       |

| T_REG2.D = ( !MODE & SDIN & !ISPEN & LOOP_IN & SHFT & STO.Q & !STI.Q & ST2.Q<br>& ST3.Q<br># !MODE & SDIN & !ISPEN & !CAI & SHFT & !STO.Q & ST1.Q & ST2.Q                                                                             |

| <pre></pre>                                                                                                                                                                                                                           |

| TREG2.CE = ( !MODE & SDIN & !CAI & ST1 & !ST2 & ST3 & TREG0 & TREG1                                                                                                                                                                   |

| T_REG1.D = ( !MODE & SDIN & !ISPEN & SHFT & STO.Q & !ST1.Q & ST2.Q & ST3.Q<br>& T_REG2.Q<br># !MODE & SDIN & !ISPEN & SHFT & !STO.Q & ST1.Q & ST2.Q & ST3.Q                                                                           |

| E T_REG2.Q<br>ISPEN & CAO & IST3 & IT_REG1 & ISHFT<br>ISPEN & CAO & IST3 & IT_REG1 & ISHFT                                                                                                                                            |

| <pre># !ISPEN &amp; CAO &amp; !STI &amp; !T REG1 &amp; !SHFT # !ISPEN &amp; CAO &amp; STO &amp; !T_REG1 &amp; !SHFT ); " ISTYPE 'BUFFER'</pre>                                                                                        |

| T_REG1.C = ( OCLK );<br>T_REG1.CE = ( !MODE & SDIN & !CAI & ST1 & !ST2 & ST3 & T_REG0                                                                                                                                                 |

| T_REGO.D = ( !MODE & SDIN & !ISPEN & SHFT & STO.Q & !STI.Q & ST2.Q & ST3.Q<br>& T REGI.Q<br># !MODE & SDIN & !ISPEN & SHFT & !STO.Q & ST1.Q & ST2.Q & ST3.Q                                                                           |

| E T REGI.Q<br># !ISPEN & CAO & !ST3 & !T REGO & !SHFT<br># !ISPEN & CAO & ST2 & !T REGO & !SHFT<br># !ISPEN & CAO & ST2 & !T REGO & !SHFT                                                                                             |

| <pre># !ISPEN &amp; CAO &amp; STO &amp; !T_REGO &amp; !SHFT ); " ISTYPE 'BUFFER' T REGO C = ( OCLK );</pre>                                                                                                                           |

| T_REGO.CE = ( !MODE & SDIN & !CAI & ST1 & !ST2 & ST3                                                                                                                                                                                  |

| <pre># ST0.Q &amp; !ST1.Q &amp; !ST2.Q &amp; ST3.Q # ISPEN );</pre>                                                                                                                                                                   |

| CAO.D = ! ( !MODE & SDIN & !ISPEN & T_REG0 & T_REG1 & T_REG2 & ST0.Q & ST1.Q                                                                                                                                                          |

| <pre></pre>                                                                                                                                                                                                                           |

| CAO.AR = ( ISPEN );<br>CAO.CE = ( !MODE & SDIN & !ISPEN & T_REGO & T_REG1 & T_REG2 & STO.Q & STI.Q                                                                                                                                    |

| <pre># !MODE &amp; SDIN &amp; !ISPEN &amp; !STO.Q &amp; STI.Q &amp; ST2.Q &amp; ST3.Q<br/># !MODE &amp; SDIN &amp; !ISPEN &amp; STO.Q &amp; !ST1.Q &amp; ST2.Q &amp; ST3.Q<br/># STO.Q &amp; !ST1.Q &amp; !ST2.Q &amp; ST3.Q );</pre> |

| PROGEN.D = ! ( !MODE & SDIN & !ISPEN & STO.Q & !STI.Q & ST2.Q & ST3.Q                                                                                                                                                                 |

23 ICAO & ISTO.Q \$ ISPEN & STO.Q SDIN & STO.Q ŧ IST3.Q IST2.Q ST1.Q ); " ISTYPE 'INVERT' ŧ ( OCLK ); ( ST0.Q & IST1.Q & IST2.Q & ST3.Q ( ST0.Q & IST1.Q & ST3.Q ); PROGEN.C PROGEN.CE = LOOP IN.OE = (0);ISPEN0 = ! ( !M\_ISPO ); ISPENO.OE = ( !ISPEN & T\_REGO & !T\_REG1 & !T\_REG2 & !PROGEN.FB ); ISPEN1 = ! ( !M\_ISP1 ); ISPEN1.OE = ( !ISPEN & !T REGO & T REG1 & !T REG2 & !PROGEN.FB ); ISPEN2 = !( !M\_ISP2 ); ISPEN2.OE = ( !ISPEN & T REGO & T REG1 & !T REG2 & !PROGEN.FB ); ISPEN3 = !( !M\_ISP3 ); ISPEN3.OE = ( !ISPEN & !T\_REGO & !T\_REG1 & T\_REG2 & !PROGEN.FB ); ISPEN4 = !( !M\_ISP4 ); ISPEN4.OE = ( !ISPEN & T\_REG0 & !T\_REG1 & T\_REG2 & !PROGEN.FB ); ISPEN5 = !( !M\_ISP5 ); ISPEN5.OE = ( !ISPEN & !T\_REG0 & T\_REG1 & T\_REG2 & !PROGEN.FB ); ISPEN6 = !( !M ISP6); ISPEN6.OE = ( !ISPEN & T\_REG0 & T\_REG1 & T\_REG2 & !PROGEN.FB ); = ( !MODE & SDIN & !ISPEN & !ST0.Q & ST1.Q & !ST2.Q & ST3.Q # !MODE & SDIN & !ISPEN & ST0.Q & !ST1.Q & ST2.Q & ST3.Q SHFT.D !SDIN & !ISPEN & STO.Q & STI.Q & !ST2.Q & ST3.Q ); \* ISTYPE 'BUFFER' SHFT.CE = ( ST0.Q & !ST1.Q & ST2.Q & ST3.Q ST1.Q & !ST2.Q & ST3.Q !ST0.Q & ST1.Q & ST3.Q ); Warning 5087: Mapping STO to STO.FB; only one fb is allowed on pin 26 Warning 5087: Mapping ST1 to ST1.FB; only one fb is allowed on pin 27 Warning 5087: Mapping ST2 to ST2.FB; only one fb is allowed on pin 28 Warning 5087: Mapping ST3 to ST3.FB; only one fb is allowed on pin 29 Warning 5087: Mapping T REGO to T REGO.FB; only one fb is allowed on pin 31 Warning 5087: Mapping T REG1 to T REG1.FB; only one fb is allowed on pin 32 Warning 5087: Mapping T REG2 to T REG2.FB; only one fb is allowed on pin 33

۱

----- F6001 Chip Diagram -----

SIGNATURE: N/A

\*

QP24\* QF8294\* QV102\* F0\* X0\* NOTE Table of pin names and numbers\* NOTE PINS OCLK:13 MODE:1 SDIN:2 ISPEN:3 CAI:4 M\_ISP0:5 M\_ISP1:6 M\_ISP2:7\* NOTE PINS M\_ISP3:8 M\_ISP4:9 M\_ISP5:10 M\_ISP6:11 LOOP\_IN:23 ISPEN0:14 ISPEN1:15\* NOTE PINS ISPEN2:16 ISPEN3:17 ISPEN4:18 ISPEN5:19 ISPEN6:20 PROGEN:21 CAO:22\* NOTE Table of node names and numbers\* NOTE NODES ST0:26 ST1:27 ST2:28 ST3:29 T\_REG0:31 T\_REG1:32 T\_REG2:33\* NOTE NODES SHFT: 30\* 11111111111111111111111111101010101111\* 1111111111111111101101110101001010111101\*

| 5,329,179                                      |          |

|------------------------------------------------|----------|

| 27 28                                          |          |

|                                                |          |

| L3534 1111101111111111111111111111111111111    |          |

| L3648 1111101111111111111111111111111111111    |          |

| 111111111111111111111111111111111111111        |          |

| L3762 1111101111111111111111111111111111111    |          |

|                                                |          |

| 1111111111111111111111111111111111111          |          |

| L3876 1111011111111111111111111111111111111    |          |

| 111111111111111111111111111111111111111        |          |

| L3990 11111011111111111111111111111111111      |          |

| 111111111111111111111111111111111111111        |          |

| L4104 1111101111111111111111111111111111       | .111111  |

| 111111111111111111111111111111111111111        |          |

| L4218 111101111111111111111111111111111111     | 1111111  |

| 111111111111111111111111111111111111111        |          |

|                                                |          |

| 111111111111111111111111111111111111111        |          |

|                                                | 1111111  |

| 111111111111111111111111111111111111111        |          |

| L4560 1110101111111111111110101100111111111    |          |

| 111111111111111111111111111111111111111        |          |

| L4674 1111111111111111111110011001111111111    |          |

| 111111111111111111111111010101111111111        |          |

|                                                | 1111111  |

| 111111111111111111111111111111111111           |          |

|                                                |          |

| 111111111111111111101011101010111111111        |          |

|                                                |          |

| 11111111111111111111111111111111111111         |          |

| 111111111111111111111111111111111111111        |          |

| L5244 1111111111111111111111100111011111111    | 1111111  |

| 111111111111111111111111111111111111111        | ******   |

| L5358 11111111111111111111111111111111111      | 111111   |

| 111111111111111111111111111111111111111        |          |

| L5472 1111011111111111111111111111111111111    | 111111   |

| 111111111111111111111111111111111111111        | ******   |

| L5586 1110111111111111111111111111111111111    | 1111111  |

| 111111111111111111111111111111111111111        |          |

| L5700 11111111011111111111111111111111111      | 1111111  |

| 1111011111111111111111111111111111             |          |

| L5814 11111111111111111111111111111111111      | 1111111  |

| 111110111111111111111111111111111111111        |          |

| L5928 111111111111111111111111111111111111     | 1111111  |

| 111111101111111111111111111111111111111        |          |

| L6042 111111111111111111111111111111111111     | 1111111  |

| 111111111011111111111111111111111111111        |          |

| L6156 1111111111111111111111111111111111       | .1111111 |

| 111111111110111111111111111111111111111        |          |

| L6270 111111111111111111111111111111111111     | .1111111 |

| 111111111111111111111111111111111111111        |          |

| L6384 111111111111111111111111111111111111     | .1111111 |

| 111111111111110111111111111111111111111        |          |

| L6498 111111111111111111111111111111111111     | .1111111 |

| 111111111111111111111111111111111111111        |          |

| L6612 11110111111111111111111111111111111      | .1111111 |

| 111111111111111111111111111111111111111        |          |

| L6726 11111111111111111111111111111111111      | 1111111  |

| 111111111111111111111111111111111111111        |          |

| L6840 111111111111111111111111111111111111     | 1111111  |

| 111111111111111111111111111111111111111        |          |

| L6954 000000000000000000000000000000000000     | 0000000  |

| 000011111111111111111111111111111111111        |          |

| L7068 00000000000000000000000000000000000      | 00000000 |

| 00001111111111111111111111111111111111         |          |

| L7182 000000000000000000000000000000000000     | 0000000  |

| 00001111111111111111111111111111111111         |          |

| L7374 111111111111111111111111111111111111     | 1111111  |

| 1111+                                          |          |

| L7452 111111111111111111111111111111111111     | [1111111 |

| 1111                                           |          |

| L7530 1111011111111111111111111111101010111111 | 11111101 |

| 1111*                                          |          |

|                                                |          |

|                | 29                                                      | 30                                      |

|----------------|---------------------------------------------------------|-----------------------------------------|

|                | 111110111111111111111111111111111111111                 | 111111001011111111111111111111111111111 |

|                | 111110111111111111111111111111111111111                 | 111110110011111111111111111111111111111 |

|                | 111110111111111111111111111111111111111                 | 111111010011111111111111111111111111111 |

|                | 111110111111111111111111111111111111111                 |                                         |

|                | 111110111111111111111111111111111111111                 | 111111001101111111111111111111111111111 |

|                | 111110111111111111111111111111111111111                 | 111110110101111111111111111111111111111 |

|                | 111101111111111111111111111111111111111                 |                                         |

| 1111*<br>L8154 |                                                         |                                         |

| L8157<br>L8160 | -                                                       |                                         |

| L8160          |                                                         |                                         |

| L8166          |                                                         |                                         |

| L8169          |                                                         |                                         |

| L8172          | 100*                                                    |                                         |

| L8175          |                                                         |                                         |

|                | 0100*                                                   |                                         |

|                | 0100*                                                   |                                         |

|                | 0100*                                                   |                                         |